Wafer-on-Wafer: el nuevo diseño de TSMC que duplicará el rendimiento de las tarjetas gráficas de NVIDIA y AMD

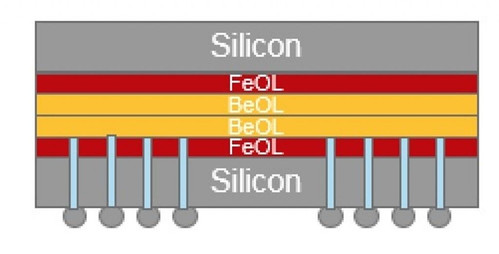

Wafer-on-Wafer (oblea sobre oblea en español) es una tecnología que funciona apilando capas verticalmente en lugar de apilarlas de manera horizontal como hasta ahora. Este tipo de planteamiento es similar al que se está aplican en la actualidad con las memorias 3D NAND, que alcanzan hasta 64 capas.

Gracias a esta pequeña pero importantísima mejora, la compañía permitirá a NVIDIA y a AMD crear tarjetas gráficas más potentes sin necesidad de aumentar el tamaño del die o tener que esperar a reducir los nanómetros de fabricación.

Este diseño pega las obleas unas con otras mediante el uso de pequeños agujeros de 10 micras que forman una conexión a través del silicio. Cadence, el socio de TSMC que ha desarrollado esta tecnología, explica que los diseños con la técnica WoW se pueden colocar en un intercalador. Este intercalador es una interfaz eléctrica que transmite la información, creando una especie de cubo de 2 dies. Con este método se pueden apilar incluso más de dos obleas de manera vertical.

También tiene sus contras: más chips desechados, más consumo y más calor

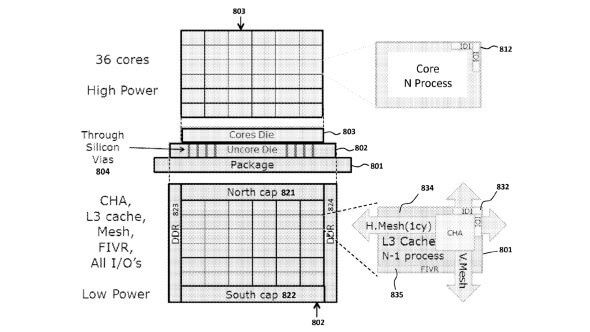

Con esta tecnología se pueden introducir más núcleos en un mismo paquete, y cada oblea puede comunicarse entre sí con una latencia mínima que compensaría el espectacular aumento de rendimiento. Con WoW podríamos ver cómo un fabricante lanza una tarjeta (por ejemplo, una GTX 1180, y más adelante saca un modelo que equipe dos dies de esta tarjeta, duplicando de manera efectiva el rendimiento y sin que el PC la detecte como dos tarjetas gráficas separadas (como ocurría con las AMD R9 295X2). Lo que sí aumentaría también es el consumo, aunque puede que no se llegase a duplicar. También habrá que ver cómo consiguen disipar el calor del chip que hay debajo.

Este diseño doble recuerda también al diseño de los EMIB de Intel o a los CCX de los AMD Ryzen con Infinity Fabric, que tiene dos complejos de núcleos que se intercomunican entre sí. Otro problema del diseño WoW es que aumentan el número de chips desechados, ya que si una de las dos obleas usadas está mal es necesario descartar el paquete completo, aunque el otro esté perfectamente.

Por ello, sería necesario que se usasen procesos con un alto nivel de fiabilidad (más del 90%), como los 16 nm de la propia TSMC. Sin embargo, la compañía afirma no tener miedo a este problema, y dice que van a aplicarlo en futuros diseños que usen tamaños de 5 y 7 nanómetros. Gracias a él, se podría llegar a acabar incluso con el SLI, o hacerlo mucho menos atractivo de cara al usuario.

Fuente: adslzone